## **Five-Lines ESD Protection -ESD5V0K5**

### Description

The ESD5V0K5 TVS arrays are designed to protect sensitive electronics from damage or latch-up due to ESD and other voltage-induced transient events. They are designed for use in applications where board space is at a premium. Each device will protect up to five lines. They are unidirectional devices and may be used on lines where the signal polarities are above ground. TVS diodes are solid-state devices designed specifically for transient suppression. They feature large cross-sectional area junctions for conducting high transient currents. They offer desirable characteristics for board level protection including fast response time.

### Feature

- Case :JEDEC SOT363 package

- Low clamping voltage

- Protects five I/O lines

- Solid-state silicon-avalanche technology

- Compatible with IEC 61000-4-2(ESD) :Air 15KV, Contact 8KV

- Compatible with IEC 61000-4-4(EFT) :40A ,5/50 nS

### Applications

- Portable Electronics

- Industrial Controls

- Wireless systems

- Security systems

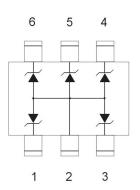

#### **Schematic & PIN Configuration**

### **Absolute Maximum Ratings**

| Parameter                              |                      | Symbol            | Limits             | Unit |

|----------------------------------------|----------------------|-------------------|--------------------|------|

| IEC61000-4-2(ESD)                      | Air                  |                   | ±15                | KV   |

|                                        | Contact              |                   | <b>±</b> 8         | 100  |

| ESD voltage                            | Per Human Body Model |                   | 16                 | KV   |

|                                        | Per Machine Model    |                   | 400                | V    |

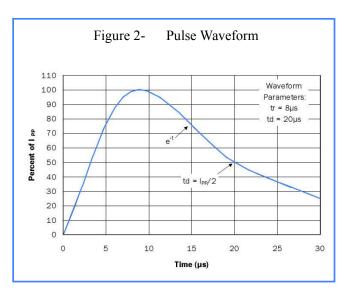

| Peak Power Dissipation @ 8 X 20 ms @TA | A ≤ 25°C (Note 1)    | $P_{pk}$          | 100                | W    |

| Steady State Power 1 Diode (Note 2)    |                      | P <sub>D</sub>    | 200                | mW   |

| Thermal Resistance Junction-to-Ambient |                      | R⊚JA              | 625                | °C/W |

| Lead Solder Temperature - Maximum (10  | Second Duration)     | $T_L$             | 260                | ℃    |

| Junction and Storage temperature range |                      | $T_{j,}\;T_{stg}$ | -55 ~ <b>+</b> 150 | ℃    |

# **Electrical Characteristics (T = 25° C)**

| Parameter                    | Symbol         | Conditions                                               | Min. | Тур. | Max. | Units      |

|------------------------------|----------------|----------------------------------------------------------|------|------|------|------------|

| Reverse Stand-off<br>Voltage | $V_{RWM}$      |                                                          |      |      | 5    | V          |

| Reverse Breakdown<br>Voltage | $V_{BR}$       | It = 1mA                                                 | 6    |      | 7.2  | V          |

| Reverse Leakage<br>Current   | I <sub>R</sub> | $V_R = V_{RWM}$                                          |      |      | 5    | μ <b>Α</b> |

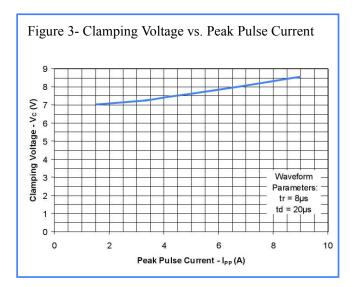

| Clamping Voltage             | Vc             | $I_{PP}$ =1A, $t_P$ = 8/20 $\mu$ s                       |      |      | 9.5  | V          |

| Clamping Voltage             | V <sub>C</sub> | $I_{PP}$ =5A, $t_P$ = 8/20µs                             |      |      | 12.5 | V          |

| Junction Capacitance         | С              | V <sub>R</sub> =0V, f = 1MHz<br>Between I/O pins and GND |      | 35   | 50   | pF         |

#### Circuit Board Layout Recommendations for Suppression of ESD.

| Circuit Bo                   | Circuit Board Layout Recommendations for Suppression of ESD. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Mode                         | Pin Connection                                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 5-line<br>protection<br>mode | 1/01 0<br>1/02 0<br>1/03 0<br>0<br>1/04 0<br>1/05 0          | Good circuit board layout is critical for the suppression of ESD induced transients. The following guidelines are recommended:  A: Place the ESD5V0K5 near the input terminals or connectors to restrict transient coupling.  B: Minimize the path length between the ESD5V0K5 and the protected line.  C: Minimize all conductive loops including power and ground loops.  D: The ESD transient return path to ground should be kept as short as possible.  E: Never run critical signals near board edges.  F: Use ground planes whenever possible. |  |  |  |  |

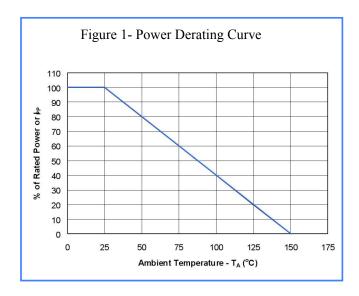

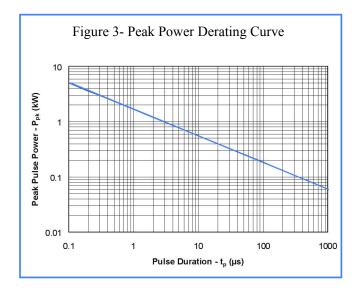

### Rating & Characteristic Curves

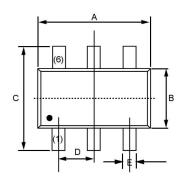

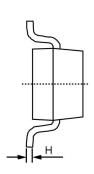

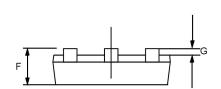

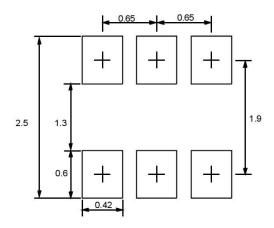

# PACKAGE OUTLINE DIMENSIONS : **SOT - 363**

| Dim | Millimeters |      | Inches   |       |  |

|-----|-------------|------|----------|-------|--|

|     | MIN         | MAX  | MIN      | MAX   |  |

| A   | 2.0         | 2.2  | 0.079    | 0.087 |  |

| В   | 1.15        | 1.35 | 0.045    | 0.053 |  |

| С   | 2.15        | 2.45 | 0.085    | 0.096 |  |

| D   | 0.65BSC     |      | 0.026BSC |       |  |

| Е   | 0.15        | 0.35 | 0.006    | 0.014 |  |

| F   | 0.90        | 1.10 | 0.035    | 0.043 |  |

| G   | 0.00        | 0.10 | 0.000    | 0.004 |  |

| Н   | 0.08        | 0.15 | 0.003    | 0.006 |  |

## Disclaimer

Specifications are subject to change without notice.

The device characteristics and parameters in this data sheet can and do vary in different applications and actual device performance may vary over time.

Unit:mm

Users should verify actual device performance in their specific applications.